和MI400系列数据中心加速器。AMD曾在2025年6月的“Advancing AI”活动上介绍过Venice和MI400系列的规格,但此次是AMD首次公开展示这两个产品线的芯片。

首先,Venice 处理器最显著的变化在于其 CCD 与 I/O 芯片的封装方式有所不同。AMD 自 EPYC Rome 以来一直使用封装的有机基板来连接 CCD 和 I/O 芯片,而 Venice 似乎采用了一种更先进的封装方式,类似于StrixHalo 或 MI250X。另一个变化是,Venice 似乎配备了两个 I/O 芯片,而不是之前 EPYC CPU 的单个 I/O 芯片。

Venice 芯片包含 8 个 CCD,每个 CCD 有 32 个核心,因此每个 Venice 封装最多可容纳 256 个核心。对每个芯片进行测量后发现,每个 CCD 的 N2 硅面积约为 165 平方毫米。如果 AMD 坚持每个核心配备 4MB 的 L3缓存,那么每个 CCD 就包含 32 个 Zen 6 核心和 128MB 的 L3 缓存,以及用于 CCD 与 I/O 芯片通信的芯片间接口。每个 CCD 的面积约为 165 平方毫米,这意味着每个 Zen 6 核心加上 4MB 的 L3 缓存大约占 5 平方毫米,这与Zen 5 核心加上 4MB L3 缓存后 N3 芯片的面积(约 5.34 平方毫米)相近。

接下来看I/O芯片,每个芯片的面积约为353平方毫米,总共超过700平方毫米的硅片用于I/O芯片。这比之前的EPYC CPU的I/O芯片面积(约400平方毫米)有了显著提升。这两个I/O芯片似乎采用了某种类似于CCD的先进封装技术。在I/O芯片旁边,封装两侧各有4个小芯片,共8个,它们可能是结构硅片或深沟槽电容芯片,旨在改善CCD和I/O芯片的供电。

我们再来看看MI400加速器。这款芯片封装尺寸巨大,包含12颗HBM4显存芯片和“12颗2纳米和3纳米制程的计算和I/O芯片”。它似乎和MI350一样,有两个基础芯片。但与MI350不同的是,MI400的基础芯片顶部和底部似乎还有两个额外的芯片。这两个额外的芯片很可能用于封装外I/O,例如PCIe、UALink等。

通过计算基础芯片和I/O芯片的面积,两个基础芯片的面积约为747平方毫米,而封装外的I/O芯片的面积约为220平方毫米。至于计算芯片,虽然封装方式使得不同计算芯片之间无法直接区分,但很可能共有8个计算芯片,每个基础芯片上集成4个计算芯片。因此,虽然我们无法确定计算芯片的确切面积,但其最大面积约为180平方毫米。计算芯片组的面积可能在140平方毫米到160平方毫米之间,但这只是最佳估计,还需要进一步验证。

Venice 和 MI400 系列都将于今年晚些时候发布,我迫不及待地想了解这两款 SoC 的底层架构。

在苏姿丰担任AMD首席执行官的十一年多时间里,该公司从Opteron的低谷中强势回归,成为数据中心Kaiyun科技有限公司CPU领域英特尔的强劲对手。这在很大程度上要归功于苏姿丰、首席技术官马克·帕珀马斯特以及其他众多团队成员推动的Zen微架构和Epyc服务器芯片的创新。而且,正如我们之前提到的,这也要归功于英特尔自身的一些失误。

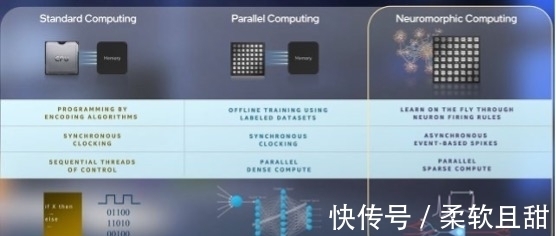

在人工智能时代,这家供应商正寻求在由行业领头羊英伟达主导的GPU系统市场中为自己开辟更大的空间。

AMD 还有很长的路要走,但它正努力将其 Instinct GPU 打造成英伟达 (Nvidia) 的有力竞争对手。它最近宣布与OpenAI建立合作关系,OpenAI 三年前凭借ChatGPT开启了当前的生成式人工智能 (AI) 潮流,并且像其竞争对手一样,也在推动智能体人工智能的发展。此次合作无疑将对 AMD 大有裨益,因为 AMD 加入了一家急需更多计算能力且似乎拥有雄厚财力的公司。此前,AMD 还与其他 AI 领域的公司建立了合作关系,包括去年早春宣布与Oracle的合作。

正是在这样的背景下,苏姿丰登台,在拉斯维加斯举行的2026年消费电子展(CES)上发表了开幕主题演讲,并指出人工智能领域对计算能力的需求正在迅速增长。她表示,AMD是最有能力、也最准备好提供这种计算能力的公司,并补充说,AMD不仅能够提供GPU和CPU,还能提供满足计算需求所需的神经处理单元(NPU)和系统架构。这种计算需求每年增长超过四倍,与更智能、更有用的模型的出现、推理能力的飞跃以及智能体的兴起保持同步。

苏姿丰表示:“要满足这种计算需求,整个生态系统必须紧密协作。我们常说,真正的挑战在于如何构建兆级人工智能基础设施?这不仅仅需要原始的性能。它始于领先的计算能力,包括CPU、GPU和网络,需要整合。它需要开放式模块化机架设计,能够随着产品世代的演进而不断升级。它需Kaiyun科技有限公司要高速网络连接,将数千个加速器连接到一个统一的系统中。而且,它必须非常易于部署。”

AMD即将推出的下一代机架式服务器平台Helios,正如CEO苏姿丰所说,是为Yotta级计算时代而设计的。它采用双宽设计,基于开放计算项目(OCP)的开放式机架宽(ORW)标准,重量接近7000磅。Helios将于今年上市,还将搭载AMD最新的AI GPU Instinct MI455X和下一代Epyc“Venice”服务器CPU,这两款产品苏姿丰都在主题演讲中进行了展示。

“如果你以前没见过机架,我告诉你,Helios 的机架简直是个庞然大物,”她说。“这可不是普通的机架,好吗?它实际上比两辆小型轿车加起来还要大。”

苏姿丰还公布了AMD未来两年的数据中心GPU路线图,首先是将于今年推出的Instinct MI455X。这款GPU插槽拥有3200亿个晶体管——比大约六个月前发布的MI355X增加了70%——采用2纳米和3纳米工艺,并配备432GB的HBM4堆叠式显存,所有组件均通过AMD的3D芯片堆叠技术连接。

MI455X 也进一步提升了 AMD GPU 的性能。随着 MI355X 的发布,AMD 芯片制造商实现了比上一代产品高出三倍的推理吞吐量。而 MI455X 的性能则比 MI355X 高出十倍。

明年,随着MI500系列显卡的发布,这一趋势将进一步加速。该显卡目前正在研发中。这款GPU将基于AMD的下一代CDNA 6架构,采用2纳米制程工艺制造,并使用速度更快的HBM4E(高带宽内存4扩展版)。她表示,这款显卡将于2027年上市,这意味着AMD在四年内实现了AI性能1000倍的提升。

苏姿丰表示:“我们把内存和GPU带宽比上一代产品提高了一倍,因此即使在机架规模下,Venice也能以全速向MI455传输数据。这实际上是协同工程的结果。我们利用Pensando的800 Gb/秒以太网芯片‘Vulcano’和‘Salina’将所有组件整合在一起,从而实现了超高带宽和超低延迟。”

苏姿丰表示:“数万个Helios机架可以扩展到整个数据中心。这意味着每个Helios机架都拥有超过18,000个CDNA5 GPU计算单元和超过4,600个Zen 6 CPU核心,可提供高达2.9 exaflops的性能。每个机架还包含31 TB的HBM4内存、业界领先的260 TB/s纵向扩展带宽以及43 TB/s的聚合横向扩展带宽,从而实现极速的数据进出。”

AMD正在向英伟达发起挑战,并且其产品路线图表明它将继续这样做。但它将面对的是一个快速发展的市场领导者。正如我们本周报道的那样,英伟达在CES上公布了其即将推出的“Rubin”GPU加速器和“Vera”基于Arm架构的服务器CPU的详细参数,更不用说其可扩展的NVLink内存架构和可扩展的Spectrum以太网互连技术,以及新的网卡和DPU了。